2021年,全球半导体产业销售总额共计5.559亿美元,其中,中国以1925亿美元的半导体销售额成为全球规模最大的区域市场。在这个千亿美元市场中,有价值数亿元的高端制造设备,也有价格几元到几十元不等的芯片。

今天,全球半导体市场的竞争格局相对稳定,在产业链各环都由市场份额占绝对优势的企业主导,这些企业凭借着极高的技术壁垒,在击退新玩家的同时也掌握着行业的发展动向。

半导体产业“牵一发而动全身”的特性导致新玩家很难凭一己之力改变行业内的某些规则,改变往往来自应用侧的真实需求。正是基于这个特性,我们所看到的半导体行业创新案例往往具备更高的可靠性。

半导体行业随着应用侧技术的发展而演进,不斯往下做的先进工艺正是因为人工智能的发展,对于计算规模和计算速度的要求在不断提高。当先进工艺走到7nm以下,芯片在物理层面的缺点逐渐显现,随之而来的是持续走高的成本投入。

由于当前几乎所有芯片大厂都将主要精力放在先进工艺研发上,产业链上中下游的配合方也都围绕先进工艺开展相应研发,然而,在突破1nm极限后,摩尔定律将由此失效,基于冯诺依曼架构的芯片技术发展将不会再依托先进工艺。

在技术快要走到极限之时,必然会提前出现“掉头”的现象,在半导体领域,“掉头”意味着在芯片从0到1的各个环节寻找新的方法突破瓶颈。

芯片领域的创新包括先进封装技术,新型架构,新材料等各个方向。在其中,我们关注到基于存算一体架构的芯片研发。在采访了部分行业头部机构后,我们希望可以还原存算一体技术的本真,并且能够一探这一领域的真正价值。

人工智能芯片是人工智能技术发展的硬件基础

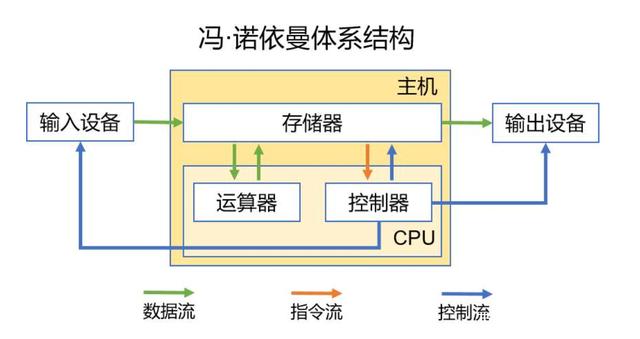

人工智能芯片是人工智能技术发展的硬件基础,在人工智能发展三大要素,数据、算法和算力中,算力主要由人工智能芯片支撑。人工智能芯片目前有两种发展路径:一种是在传统计算架构下的A加速器/针算卡,主要以GPU, FPGA ASIC等为代表;另一种路径是颠覆传统的冯诺依曼架构,采用新的架构来提升计算能力,以存算一体芯片为代表。

当前,摩尔定律已派近极限,依靠器件尺寸微缩来提高芯片性能的技术路径在功耗和可靠性方面都面临巨大挑战。传统的冯诺依曼架构已无法适应如今Al计算对算力和低功耗的需求,存算一体芯片架构是需求变化中催生出的新型计算架构,在算力和能效比方面相比冯诺依曼架构具有绝对优势。

存算一体是将存储单元和计算单元合为一体,省去了计算过程中数据搬运环节,消除了由于数据搬运带来的功耗和延迟,有望彻底解决传统冯诺伊曼架构的存储墙问题,极大提高计算能效。由于实现形式不同,目前业内对于存内计算的概念并没有形成非常明确的定义。

过去几十年,半导体行业都是按照摩尔定律在发展

过去几十年,半导体行业都是按照摩尔定律在发展。摩尔定律的核心内容是“集成电路上可以容纳的晶体管数目大约每经过18个月便会增加一倍”。在摩尔定律能够持续往下走的时候,每一到两年换一代芯片工艺,整体性能便可提升数倍,成本也会自然降低。在性能提升速度非常快的前提下,产业界不需要进行架构创新便可以不断开拓新的市场空间。

到2010年以后,进入后摩尔时代,人们意识到摩尔定律会走到极限,自2012年以来,AI训练任务的算力需求每3.5个月就会翻倍,这个数字远超过摩尔定律的18月,为了满足算力需求,芯片需要更高的集成度,晶体管的体积变得越来越小。当小到一定程度时(逼近物理极限),便会引发现新现象,如量子隧穿效应。

在冯诺依曼架构下,即使处理器的算力能够做到非常大,但存储器的访问速度远比不上处理器的处理速度,导致处理器的实际性能受到严重制约,当前针对算力需求出现了很多解决方案,如先进工艺、3D堆鲁技术等,但这些技术依旧是基于冯诺依曼架构下,仍无法从底层突破瓶颈,很快也会面临技术走到极限的问题。

当前最先进的计算机采用的都是冯诺依曼架构。在这种架构下,数据的处理和存储是分离的,分别由中央处理器CPU和存储器完成。每次执行运算时,需要把数据从存储器搬运到处理器,中间经过数据总线,当数据处理完之后再将其搬回存储器中。

冯诺依曼理论模型的重要假设之一是计算与存储速度相当,如果双方一旦在速度上不匹配,慢的一方将会制约整体计算效率,随着半导体产业的发展,处理器和存储器针对不同的用户需求形成了不同的工艺路线,速度快成为处理器的发展方向,存储器则强调大容量和低功耗,导致处理器的运行速度远快于存储器。

随着人工智能技术爆发,计算机每天要在处理器和存储器之间进行高频数据传递,产生大量功耗。谷歌2018年对其产品耗能情况展开调研,结果显示系统能耗的62.7%浪费在CPU和内存的读写传输上。

在数据传递过程中,内存的传输速度跟不上CPU性能,会导致实际算力受限,影响CPU运行处理速度。假设CPU处理运算一道指令的耗时为1ns, 内存读取传输该指令的耗时大约在10ns. 上述问题所导致的散热需求增加、用电成本上升以及算力浪费都是企业在人工智能技术发展中面临的瓶颈。

面对数据搬运产生的高能耗和存算分离导致的性能瓶颈,存算一体架构能够从根本上解决冯诺依曼瓶颈。存算一体是在存储器内嵌入计算能力,以新的架构进行二维或三维矩阵运算。这种直接利用存储器进行数据处理的方式,消除/缩小了计算单元和存储单元之间的距离,从而解决冯诺依曼瓶颈。

免责声明:本文是转载,版权归原作者所有。所以注明转载来源。本文所用视频、图片、文字如涉及作品版权问题,请第一时间告知,我们将立即删除内容!本文内容为原作者观点,并不代表本站赞同其观点和对其真实性负责。